فهرست مطالب

عنوان صفحه

آزمایش

اول: آشنایی با نرم افزار HSPICE 5

1-1 پیش آگاهی 5

1-2 دستور کار 5

1-3 سوالات 5

آزمایش دوم: پیاده سازی وارون کننده افزایشی با

قطعه CD4007 6

2-1 پیش آگاهی 6

2-2 دستور کار 6

2-3 سوالات 7

آزمایش سوم: رفتار تکنولوژی های مختلف در حالت بی بار 8

3-1 پیش آگاهی 8

2-3 دستور کار 8

3-3 سوالات 8

آزمایش چهارم: رفتار تکنولوژی های مختلف در حالت با

بار 9

4-1 پیش آگاهی 9

4-2 دستور کار 9

4-3 سوالات 10

آزمایش پنجم: محاسبه تاخیر در تکنولوژی های مختلف 11

5-1 پیش آگاهی 11

5-2 دستور کار 11

5-3 سوالات 12

آزمایش ششم: مشخصات و رفتار پویای وارون کننده CMOS 13

6-1 پیش آگاهی 13

6-2 دستور کار 13

6-3 سوالات 13

آزمایش هفتم: بررسی رفتار وارون کننده CMOS با خروجی Tri-State 14

7-1 پیش آگاهی 14

7-2 دستور کار 14

7-3 سوالات 14

آزمایش هشتم: پیاده سازی مدارهای مختلف 15

8-1 پیش آگاهی 15

8-2 دستورکار 15

8-3 سوالات 15

آزمایش نهم : پیاده سازی یک شمارنده 8 بیتی در HSPICE 16

9-1 پیش آگاهی 16

9-2 دستور کار 16

9-3 سوالات 16

آزمایش دهم : پیاده سازی یک ضرب کننده 4×4 در HSPICE 18

10-1 پیش آگاهی 18

10-2 دستور کار 18

10-3 سوالات 18

در این آزمایش ابتدا با نرم افزار

HSPICE و

دو تکنولوژی معروف و مورد استفاده CMOS و CNTFET آشنا خواهید شد.

بخش الف:

یک گیت XOR دو ورودی، AND دو ورودی، OR سه ورودی Pull up-Pull down با

استفاده از کتابخانه 180 CMOS در نرم افزار HSPICE شبیه سازی کنید.

بخش ب:

یک گیت XOR دو ورودی، XOR سه ورودی، AND دو ورودی، AND سه ورودی، OR سه ورودی Pull up-Pull down با

استفاده از کتابخانه CNTFET در نرم افزار HSPICE شبیه سازی کنید.

بخش ج:

یک Full adder با استفاده

از گیت های طراحی شده در قسمت الف و کتابخانه 180 CMOS در نرم

افزار HSPICE

شبیه سازی کنید.

بخش د:

یک Full adder با استفاده

از گیت های طراحی شده در قسمت ب و کتابخانه CNTFET در نرم

افزار HSPICE

شبیه سازی کنید.

1.

تاخیر، توان مصرفی و حاصل ضرب توان در تاخیر (PDP) دو قسمت ج

و د را محاسبه کنید.

2.

دو تکنولوژی CNTFET و CMOS را با یکدیگر مقایسه کنید.

3.

هدف از این آزمایش آشنایی با قطعه

CD4007 و

به دست آوردن دو پارمتر ولتاژ آستانه و ضریب عبور ترانزیستور به صورت عملی است.

2-1-1 قطعه CD4007

قطعه CD4007 دارای سه

وارون کننده CMOS است که می توان از PMOS و NMOS های هر وارون کننده به صورت جداگانه نیز استفاده نمود. قابل

ذکر است که این تراشه همانند تراشه های دیگر حساس بوده و توصیه می شود از جابه

جایی و اتصالات اضافی به آن خودداری کنید.

بخش الف: تعیین ولتاژ آستانه

ترانزیستور NMOS

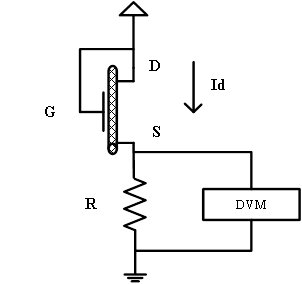

ابتدا یک مدار که دارای یک

ترانزیستور NMOS و یک مقاومت (به اندازه دلخواه) به همراه منبع تغذیه همانند شکل

(1) ببندید. عملکرد این مدار را قبل از تحلیل نتایج بررسی کنید. سپس منبع تغذیه را

به فاصله 0.2 از 0 تا 5 ولت افزایش دهید، زمانی که یک جریان Id در

مقاومت دیده شود، منبع تغذیه نشان دهنده ولتاژ آستانه (Vt)

است.

بخش ب: تعیین ولتاژ آستانه

ترانزیستور PMOS

بخش الف را برای مداری همانند شکل

(1) که به جای ترانزیستور NMOS آن از یک ترانزیستور PMOS استفاده شده است، تکرار تمائید. و Vt آن

را محاسبه کنید.

بخش ج: تعیین ضریب عبور

ترانزیستور NMOS

برای تعیین ضریب عبور ترانزیستور

(K)

از مقدار

جریان Id و فرمول آن (Id = K(Vds - Vt )) استفاده می شود. در واقع با استفاده از مقدار مقاومت و قانون

اهم که برای محاسبه میزان افت ولتاژ دو سر مقاومت استفاده می شود و فرمول Id = K(Vds - Vt) مقدار K محاسبه می

شود. (ضریب K را

برای مقدار مقاومت های مختلف به دست آورید و نتیجه را تحلیل کنید)

بخش د: تعیین ضریب عبور

ترانزیستور PMOS

بخش ج را برای مداری همانند شکل

(1) که به جای ترانزیستور NMOS آن از یک ترانزیستور PMOS استفاده شده است، تکرار نمائید. و K آن را

محاسبه کنید.

1- نتایجی که در بخش های الف تا د به دست

آورده اید با مقادیری که در datasheet این قطعه ذکر شده است، مقایسه کنید.

|

|

|

شکل

(1)

|

هدف از این آزمایش آشنایی با

ویژگی های تکنولوژی های مختلف (وارون کننده NMOS، وارون

کننده افزایشی (NMOS)، وارون کننده افزایشی (PMOS) و وارون کننده CMOS (Pull up-Pull down)) در حالت بدون بار است. در نهایت، رفتار عملی را با آن چه در تئوری آموخته اید، مقایسه

خواهید کرد.

بخش الف:

با استفاده از قطعه CD4007،

منبع تغذیه 5 ولت و یک مقاومت 10 کیلو اهم یک مدار وارون کننده NMOS طراحی و پیاده سازی کنید. سپس مقادیر VOH، VOL، VIH و VIL را

برای آن به دست آورید. (این آزمایش را برای دو مقدار مقاومت 1 و 100 کیلو اهم نیز

تکرار کنید و نتایج را مقایسه کنید)

بخش ب:

بخش الف را برای مدار وارون کننده

افزایشی (NMOS) تکرار نمائید.

بخش ج:

بخش الف را برای مدار وارون کننده

افزایشی (PMOS) تکرار نمائید.

بخش د:

بخش الف را برای مدار وارون کننده

CMOS (Pull up-Pull down) تکرار نمائید.

1.

مقادیر VOH، VOL، VIH و VIL چهار بخش الف تا د را با یکدیگر مقایسه کنید.

هدف از این آزمایش آشنایی با

ویژگی های تکنولوژی های مختلف (وارون کننده NMOS، وارون

کننده افزایشی (NMOS)، وارون کننده افزایشی (PMOS) و وارون کننده CMOS (Pull up-Pull down))

در حالت با بار است. در

نهایت، رفتار عملی را با آن چه در تئوری آموخته اید، مقایسه خواهید کرد.

بخش الف:

دو مدار مشابه بخش الف

آزمایش 3 را به صورت cascading طراحی و شبیه سازی کنید. سپس مقادیر VOH، VOL، VIH و VIL را

برای وارون کننده اول به دست آورید. (این آزمایش را برای دو مقدار مقاومت 1 و 100

کیلو اهم نیز تکرار کنید و نتایج را مقایسه کنید)

بخش ب:

دو مدار مشابه بخش ب

آزمایش 3 را به صورت cascading طراحی و شبیه سازی کنید. سپس مقادیر VOH، VOL، VIH و VIL را

برای وارون کننده اول به دست آورید. (این آزمایش را برای دو مقدار مقاومت 1 و 100

کیلو اهم نیز تکرار کنید و نتایج را مقایسه کنید)

بخش ج:

دو مدار مشابه بخش ج

آزمایش 3 را به صورت cascading طراحی و شبیه سازی کنید. سپس مقادیر VOH، VOL، VIH و VIL را

برای وارون کننده اول به دست آورید. (این آزمایش را برای دو مقدار مقاومت 1 و 100

کیلو اهم نیز تکرار کنید و نتایج را مقایسه کنید)

بخش د:

دو مدار مشابه بخش د

آزمایش 3 را به صورت cascading طراحی و شبیه سازی کنید. سپس مقادیر VOH، VOL، VIH و VIL را

برای وارون کننده اول به دست آورید. (این آزمایش را برای دو مقدار مقاومت 1 و 100

کیلو اهم نیز تکرار کنید و نتایج را مقایسه کنید)

1.

نتایج بخش الف تا د آزمایش 3 و 4 را با یکدیگر مقایسه و نتایج حاصل

را تحلیل کنید.

هدف از این آزمایش به دست آوردن دو

تاخیر TPLH و TPHL و مقایسه نتایج در حالت تئوری و عملی است. جهت

بررسی

مشخصات

پویای

این

وارون

کننده

از

همان

مدار cascade موجود

در

آزمایش 4

استفاده کنید. برای اندازه گیری تاخیر این وارون کننده با استفاده از

oscilloscope باید تغییرات ورودی و خروجی را به صورت متناوب تکرار کنید.

در ابتدا باید یک شکل موج مربعی با فرکانس مناسب با استفاده از function generator تولید کرد و به ورودی

مدار cascade

شده اعمال کرد. بر اساس شکل موج خروجی وارون کننده اول که بر روی oscilloscope

مشاهده می کنید، مقادیر TPLH و TPHL را به دست آورید.

بخش الف:

TPLH و TPHL را

برای خروجی وارون کننده اول بخش الف آزمایش 4 به دست آورید. آیا این دو

مقدار یکسان هستند یا خیر؟ شرح دهید. فرکانس مورد استفاده را ذکر نمایید. با

استفاده از datasheet مربوطه مقدار Cin را برداربد و به صورت تئوری مقادیر TPLH و

TPHL محاسبه کنید. نتایج حاصل از تئوری و عملی را با هم مقایسه کنید.

بخش ب:

TPLH و TPHL را

برای خروجی وارون کننده اول بخش ب آزمایش 4 به دست آورید. آیا این دو مقدار

یکسان هستند یا خیر؟ شرح دهید. فرکانس مورد استفاده را ذکر نمایید. به صورت تئوری

مقادیر TPLH و TPHL محاسبه کنید. نتایج حاصل از تئوری و عملی را با هم مقایسه کنید.

بخش ج:

TPLH و TPHL را

برای خروجی وارون کننده اول بخش ج آزمایش 4 به دست آورید. آیا این دو مقدار

یکسان هستند یا خیر؟ شرح دهید. فرکانس مورد استفاده را ذکر نمایید. به صورت تئوری

مقادیر TPLH و TPHL محاسبه کنید. نتایج حاصل از تئوری و عملی را با هم مقایسه کنید.

بخش د:

TPLH و TPHL را

برای خروجی وارون کننده اول بخش د آزمایش 4 به دست آورید. آیا این دو مقدار

یکسان هستند یا خیر؟ شرح دهید. فرکانس مورد استفاده را ذکر نمایید. مقادیر TPLH و

TPHL به صورت تئوری محاسبه کنید. نتایج حاصل از تئوری و عملی را با هم

مقایسه کنید.

5-3

سوالات

1.

نتایج عملی بخش الف تا د را با یکدیگر

مقایسه کنید. کدام تکنولوژی از نظر تاخیر بهتر عمل می کند.

هدف از این آزمایش بررسی

تاثیر پارامترهای ولتاژ تغذیه و خازن بار بر روی رفتار زمانی یک وارون کننده CMOS است.

بخش الف: بررسی تاثیر Vdd بر

روی تاخیر

مدار بخش د آزمایش شماره 5

را ببندید و دو مقدار TPLH و TPHL را به ازای مقادیر منبع تغذیه از 4 تا 10 ولت و به فاصله 1 ولت

محاسبه کنید. از نظر تئوری افزایش Vdd بر روی تاخیر چه تاثیری دارد؟ آیا این تاثیر در نتایج عملی نیز

دیده می شود.

بخش ب: بررسی تاثیر خازن بار بر

روی تاخیر

به جای مدار وارون کننده دوم در

بخش الف، خازن های 50 پیکوفاراد در خروجی وارون کننده اول قرار دهید و به

ازای Vdd = 5v مقادیر TPLH و TPHL را به دست آورید. آزمایش را برای خازن بار با مقادیر 100 پیکو و

200 پیکو فاراد تکرار کنید. نتایج حاصل را با یکدیگر مقایسه کنید و اثر افزایش خازن

بار بر روی تاخیر را شرح دهید.

1-

برای کاهش تاخیر چه راه حل هایی پیشنهاد می کنید.

در این آزمایش رفتار و

مشخصات یک وارون کننده CMOS با خروجی Tri-State مورد بررسی قرار می گیرد.

بخش الف:

با استفاده از ترانزیستورهای PMOS و NMOS موجود در

قطعه CD4007 و

منبع تغذیه 5 ولت (Vdd) یک وارون کننده CMOS با خروجی Tri-State بسازید. (ترانزیستورهای وارون کننده نزدیک خروجی و ترانزیستورهای

جدا کننده را در بالا و پایین قرار دهید).

همانند آزمایش 3 مقادیر VOH، VOL، VIH و VIL را

برای مدار محاسبه کنید. سپس یک خازن 100 پیکو فاراد در خروجی مدار قرار دهید و دو

مقدار TPLH و

TPHL را به دست آورید.

بخش ب:

بخش الف را برای حالتی که

جای ترانزیستورهای وارون کننده و جدا کننده با یکدیگر عوض شده اند (برای این کار

می توانید جای ورودی ها را فقط عوض کنید)، تکرار کنید.

1-

نتایج دو قسمت الف و ب را با یکدیگر مقایسه کنید.

2-

نتایج بخش الف را با نتایج یک وارون کننده CMOS معمولی

(بخش د آزمایش 4 و 5) مقایسه کنید.

آشنایی

با نحوه پیاده سازی مدارهای مختلف

بخش الف:

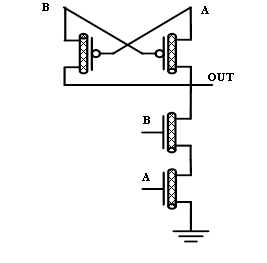

در ابتدا عملکرد مدار شکل

(2) را شرح دهید. سپس مدار را پیاده سازی کنید و مقادیر VOH، VOL را

برای خروجی محاسبه کنید. در نهایت، یک خازن به اندازه 100

پیکو فاراد در خروجی آن قرار دهید تا دو مقادیر TPLH و TPHL را

به دست آورید.

بخش ب:

مدار معادل شکل (2) را با

استفاده از روش CMOS (Pull up-Pull down) رسم و پیاده سازی نمائید. سپس مقادیر VOH، VOL را

برای خروجی محاسبه کنید. در نهایت، یک خازن به اندازه 100

پیکو فاراد در خروجی آن قرار دهید تا دو مقادیر TPLH و TPHL را

به دست آورید.

1.

نتایج دو بخش الف و ب را با یکدیگر مقایسه

کنید.

|

|

شکل (2)

|

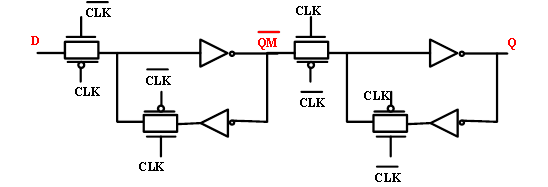

هدف از این آزمایش پیاده

سازی یک مدار بزرگ بر اساس ماژول ها در نرم افزار HSPICE است. شبیه

سازی تمام مدارها با تکنولوژی 180 نانومتر و ولتاژ تغذیه 1.8 ولت انجام شود.

بخش الف:

ابتدا مدار شکل (3) که

نشان دهنده مدار DFF است را در HSPICE طراحی و شبیه سازی کنید.

بخش ب:

با استفاده از مدار شکل (3)

یک رجیستر 8 بیتی طراحی و شبیه سازی کنید.

بخش ج:

با استفاده از ماژول Full adder

طراحی شده در آزمایش 1، یک incrementor (جمع کننده آبشاری) 8 بیتی طراحی کنید.

بخش د:

با استفاده از رجیستر 8

بیتی طراحی شده در بخش ب و مدار incrementor طراحی شده در بخش ج

یک شمارنده افزایشی 8 بیتی طراحی کنید.

1.

تاخیر، میانگین توان مصرفی، و حاصل ضرب توان در تاخیر (PDP)

شمارنده افزایشی 8 بیتی طراحی شده در بخش د را محاسبه کنید.

|

|

|

شکل (3)

|

هدف از این آزمایش پیاده

سازی یک مدار بزرگ بر اساس ماژول ها در نرم افزار HSPICE است. شبیه

سازی تمام مدارها با تکنولوژی 180 نانومتر و ولتاژ تغذیه 1.8 ولت انجام شود.

ابتدا یک مدار برای ضرب

کننده 4×4 طراحی کنید. (انتخاب نوع ضرب کننده به اختیار دانشجو است). سپس این مدار

را در HSPICE

شبیه سازی کنید. می توانید از Full

adder و جمع کننده آبشاری طراحی شده در

بخش ج آزمایش 9 استفاده کنید.

1.

تاخیر، میانگین توان مصرفی، و حاصل ضرب توان در تاخیر (PDP)

ضرب کننده 4×4 طراحی شده محاسبه کنید.

به یاد داشته باشید "یک مهندس راهی

خواهد یافت یا راهی خواهد ساخت"

موفق باشید.